別紙添付の書類に記載されている事項は下記の出願書類に記載されて いる事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日 Date of Application:

2001年 9月26日

出 願 番 号 Application Number:

特願2001-294482

出 願 人 applicant(s):

株式会社日立製作所

# CERTIFIED COPY OF PRIORITY DOCUMENT

2001年12月21日

特許庁長官 Commissioner, Japan Patent Office 及川耕

【書類名】

特許願

【整理番号】

Y3358

【提出日】

平成13年 9月26日

【あて先】

特許庁長官殿

【国際特許分類】

H01L 21/66

【発明者】

【住所又は居所】

神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生産技術研究所内

【氏名】

奥田 浩人

【発明者】

【住所又は居所】

神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生產技術研究所内

【氏名】

髙木 裕治

【発明者】

【住所又は居所】

神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生産技術研究所内

【氏名】

大島 良正

【発明者】

【住所又は居所】

神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生産技術研究所内

【氏名】

小野 眞

【発明者】

【住所又は居所】

神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生産技術研究所内

【氏名】

渡辺 正浩

【発明者】

【住所又は居所】

神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生産技術研究所内

【氏名】

前田 俊二

## 特2001-294482

【発明者】

【住所又は居所】 神奈川県横浜市戸塚区吉田町292番地 株式会社 日

立製作所 生産技術研究所内

【氏名】

野口 稔

【特許出願人】

【識別番号】

000005108

【氏名又は名称】

株式会社 日立製作所

【代理人】

【識別番号】

100093492

【弁理士】

【氏名又は名称】 鈴木 市郎

【電話番号】

03-3591-8550

【選任した代理人】

【識別番号】

100078134

【弁理士】

【氏名又は名称】 武 顕次郎

【電話番号】 03-3591-8550

【先の出願に基づく優先権主張】

【出願番号】

特願2001-45490

【出願日】

平成13年 2月21日

【手数料の表示】

【予納台帳番号】 113584

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 0011847

要

【プルーフの要否】

## 【書類名】 明細書

【発明の名称】 電子回路パターンの欠陥検査管理システム,電子回路パターンの欠陥検査システム及び装置

## 【特許請求の範囲】

【請求項1】 半導体ウエハ上に形成された電子回路パターンの欠陥検査管理システムにおいて、

被検査対象領域を検査条件が異なる少なくとも2個以上の部分検査領域に分割 する検査領域設定手段と、

該検査領域設定手段によって設定された各部分検査領域に対して、検査条件を 設定する検査条件設定手段と、

該検査領域設定手段によって設定された各部分検査領域に対して、該検査条件 設定手段によって設定した検査条件で検査を実行する検査実行手段と

を有することを特徴とする電子回路パターンの欠陥検査管理システム。

【請求項2】 請求項1記載の電子回路パターンの欠陥検査管理システムにおいて、

前記検査領域設定手段は、レイアウトパターンに基づいて、前記被検査対象領域を分割することを特徴とする電子回路パターンの欠陥検査管理システム。

【請求項3】 請求項1記載の電子回路パターンの欠陥検査管理システムにおいて、

前記検査領域設定手段は、レイアウトデータに基づいて、前記被検査対象領域 をセル部と非セル部に分割することを特徴とする電子回路パターンの欠陥検査管 理システム。

【請求項4】 半導体ウエハ上に形成された電子回路パターンの欠陥検査管理システムにおいて、

被検査対象領域の場所毎に固有の検査条件を算出する検査条件設定手段と、

該被検対象領域を、該検査条件算出手段によって算出された検査条件が同等の 部分検査領域に分割する検査領域設定手段と、

該検査領域設定手段によって設定された各部分検査領域に対して、該検査条件 設定手段によって設定された検査条件で検査を実行する検査実行手段と を有することを特徴とする電子回路パターンの欠陥検査管理システム。

前記検査領域設定手段は、少なくとも、欠陥の位置の分布を表わす欠陥分布マップ、またはレイアウトパターン、または前記検査対象領域の検出画像のいずれか1つ以上と検査領域設定状態とをオーバレイ、もしくは同時に表示する表示画面を有することを特徴とする電子回路パターンの欠陥検査管理システム。

【請求項6】 請求項1~4のいずれか1つに記載の電子回路パターンの欠陥検査管理システムにおいて、

前記検査領域設定手段は、前記被検査対象領域を欠陥出力領域と非出力領域とに分割し、

前記検査実行手段は、前記検査領域設定手段によって設定された該欠陥出力領域に属する欠陥のみを出力することを特徴とする電子回路パターンの欠陥検査管理システム。

【請求項7】 請求項1~4のいずれか1つに記載の電子回路パターンの欠 陥検査管理システムにおいて、

前記検査領域設定手段は、レイアウトデータを参照して前記被検査領域をセル 部と非セル部とに分割し、

前記検査実行手段は、欠陥のない該セル部の画像を検出して、セル部参照画像 として記憶し、

ユーザが指定した検査対象位置毎に画像を検出して欠陥画像とし、

該非セル部では、該検査対象位置毎に隣接するチップの同一パターンの箇所を 参照画像として検出し、該欠陥画像と参照画像とを比較して欠陥を抽出し、

該セル部では、該検査対象位置によらず、該セル部の参照画像と該欠陥画像と を比較して欠陥を抽出することを特徴とする電子回路パターンの欠陥検査管理システム。

【請求項8】 半導体ウエハ上に形成された電子回路パターンの欠陥情報を 管理する欠陥検査管理システムにおいて、

該半導体ウエハ上の欠陥位置座標と属性とを求める欠陥抽出手段と、

被検査対象領域を欠陥管理基準が異なる複数の部分検査領域に分割する検査領域設定手段と、

該欠陥管理基準が異なる該部分検査領域毎に欠陥管理基準を設定する欠陥管理 基準設定手段と、

該欠陥抽出手段で求めた欠陥位置座標に対して、該欠陥管理基準設定手段によって設定された該欠陥管理基準と該欠陥の属性とに基づいて、欠陥毎に管理情報を付与する欠陥分類手段と

を有することを特徴とする電子回路パターンの欠陥検査管理システム。

【請求項9】 請求項8記載の電子回路パターンの欠陥検査管理システムにおいて、

前記欠陥抽出手段は、少なくとも欠陥の位置座標とサイズを算出し、

前記欠陥管理基準設定手段は、レイアウトデータに基づいて前記被検査対象領域の各位置における致命欠陥判定サイズを算出し、

前記欠陥分類手段は、前記欠陥抽出手段で算出した欠陥位置座標に対して、前記管理基準設定手段によって設定した致命欠陥判定サイズと欠陥のサイズとを比較し、欠陥毎に致命か否かを示す管理情報を付与することを特徴とする電子回路パータンの欠陥検査管理システム。

【請求項10】 半導体ウエハ上に形成された電子回路パターンの欠陥検査 システムにおいて、

電子回路パターンのレイアウトデータに基づいて、被検査領域を検査条件が異なる複数の部分検査領域に分割する検査領域設定手段と、

該検査領域設定手段によって設定された該各部分検査領域に対して、検査条件 を設定する検査条件設定手段と、

該検査領域設定手段によって設定された該各部分検査領域を夫々、該検査条件 設定手段によって設定した検査条件で検査を実行する検査実行手段と

を有することを特徴とする電子回路パターンの欠陥検査システム。

【請求項11】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、前記レイアウトデータに基づいて被検査領域に含ま

れる各機能ブロックの範囲を算出して前記部分検査領域とすることを特徴とする 電子回路パターンの欠陥検査システム。

【請求項12】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、前記レイアウトデータに基づいて被検査領域における配線密度の分布を算出し、算出した配線密度を同じくする領域に該被検査領域を分割して前記部分検査領域とすることを特徴とする電子回路パターンの欠陥検査システム。

【請求項13】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、被検査領域を致命度の異なる部分検査領域に分割することを特徴とする電子回路パターンの欠陥検査システム。

【請求項14】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、検査領域設定画面上に、チップ全面のレイアウトパターンを表示し、さらに、該レイアウトパターン上でユーザが指定した領域を前記部分検査領域として登録する、あるいは、前記検査領域設定手段が算出した前記部分検査領域をユーザが編集して登録することを特徴とする電子回路パターンの欠陥検査システム。

【請求項15】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、前記各部分検査領域と前記レイアウトパターンとを重ね合わせて表示することを特徴とする電子回路パターンの欠陥検査システム。

【請求項16】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、前記各部分検査領域と前記レイアウトパターンと欠陥の発生位置との少なくとも2つ以上を重ね合わせて表示することを特徴とする電子回路パターンの欠陥検査システム。

【請求項17】 請求項16記載の電子回路パターンの欠陥検査システムに

おいて、

前記検査実行手段は、検出した欠陥を欠陥種によって分類し、

前記検査領域設定手段は、前記レイアウトパターン上での該欠陥の発生位置を 、欠陥種毎に異なるシンボルでもって、前記レイアウトパターンと重ね合わせて 表示することを特徴とする電子回路パターンの欠陥検査システム。

【請求項18】 請求項17記載の電子回路パターンの欠陥検査システムにおいて、

前記検査実行手段は、検出した欠陥を、少なくとも実欠陥か虚報かによって分類することを特徴とする電子回路パターンの欠陥検査システム。

【請求項19】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査実行手段は、前記レイアウトデータを参照して、検出した各欠陥に対する欠陥位置のレイアウト情報を付与し、該各欠陥の該レイアウト情報による分類を行なうことを特徴とする電子回路パターンの欠陥検査システム。

【請求項20】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査条件設定手段は、特定パターンに対して固有の検査条件を設定し、

前記検査実行手段は、前記レイアウトデータを参照して、前記検査条件設定手段によって設定した特定パターンに相当するか否かを判断し、特定パターンに相当する場合には、前記検査条件設定手段によって設定された該固有の検査条件により、検査することを特徴とする電子回路パターンの欠陥検査システム。

【請求項21】 請求項10記載の電子回路パターンの欠陥検査システムにおいて、

前記検査領域設定手段は、被検査領域をセル部と非セル部に分割し、

前記検査実行手段は、該セル部では、欠陥画像と参照画像とを検出,比較して 欠陥を検出し、該非セル部では、参照画像を検出せず、欠陥画像のみを検出して 欠陥を検出することを特徴とする電子回路基板検査装置。

【請求項22】 請求項16~18記載の電子回路パターンの欠陥検査システムの欠陥検査装置であって、

欠陥位置を1チップ分重ね合わせて表示することを特徴とする電子回路パターンの欠陥検査装置。

【請求項23】 半導体ウエハ上に形成された電子回路基板の電子回路パターンの欠陥検査システムにおいて、

該電子回路基板上の機能ブロック毎の検査パラメータを記憶する検査パラメータデータベースと、

レイアウトデータに基づいて、該電子回路基板上の被検査領域を検査条件が異なる複数の機能ブロックに分割する検査領域設定手段と、

該検査領域設定手段で分割された該機能ブロックに対し、該検査パラメータデータベースから検査パラメータを検索して設定する検査条件設定手段と、

該検査領域設定手段によって設定された該各機能ブロックに対し、該検査条件 設定手段によって設定した該検査条件で検査を実行する検査実行手段と

を有することを特徴とする電子回路パターンの欠陥検査システム。

【請求項24】 半導体ウエハ上に形成された電子回路パターンの欠陥検査 システムにおいて、

レイアウトデータに基づいて被検査領域を検査条件が異なる複数の部分検査領域に分割する検査領域設定手段と、

該検査領域設定手段によって設定された該各部分検査領域に対し、検査条件の 初期値、検査条件の調整ルール並びに検査条件の収束条件を設定する検査条件設 定手段と、

該半導体ウエハ上の該被検査領域の画像を検出する画像検出手段と、

各部分検査領域において、該画像検出手段によって検出した画像を、該検査領域設定手段により、該各部分検査領域毎の画像に分割して、該検査条件の初期値を用いて処理し、該各部分検査領域毎に欠陥を検知する検査実行手段と、

欠陥個所の画像を記憶する画像記憶手段と

を有することを特徴とする電子回路パターンの欠陥検査システム。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、半導体ウエハ上に形成された電子回路パターンの欠陥を検査するパターン検査装置に係り、特に、レイアウトデータなどの設計情報に基づいて、パターン検査装置での検査パラメータ(検査条件)の設定工数を低減し、さらには、パターン検査装置で検出した欠陥情報の管理をする電子回路パターンの欠陥検査・ステム及び装置に関する。

[0002]

## 【従来の技術】

半導体製品寿命の短縮化とシステムLSIを中心とする多品種生産体制への移行が進む中、量産プロセス条件の早期確立への要求が一層強まっている。半導体製造の各工程において、外観を検査し、欠陥の発生状態に関する情報を取得し、プロセス条件の調整の指針を得る、あるいはプロセス状態の不具合を検知するためのツールとして、欠陥検査装置は極めて重要である。既に実用化されている半導体外観検査装置としては、光学式異物検査装置、光学式あるいは電子線式のパターン検査装置や欠陥レビュー装置がある。

#### [0003]

半導体ウエハ上に形成された電子回路パターンの欠陥を検査するための従来例としては、例えば、特開昭62-43505号公報に記載されたような光学式ウエハ欠陥検査装置や特開平10-135288号公報に記載されたような電子線式欠陥レビュー装置が知られている。ユーザは、これらの欠陥検査装置を用いて電子回路パターンの欠陥検査する際、光学系の設定条件など、各種の検査パラメータを設定し、調整する必要がある。以下では、これらの検査装置における検査の概要を述べた上で、検査パラメータの設定について説明する。

#### [0004]

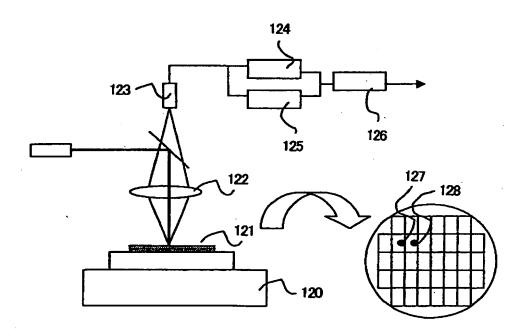

まず、第1の従来技術例として、光学式の欠陥検査技術について図22を用いて説明する。

#### [0005]

同図において、まず、ステージ120に被検査対象物である半導体ウエハ12 1を固定し、ステージ120を移動させながら、半導体ウエハ121の表面を光 走査する。この半導体ウエハ121の表面からの反射光は検出光学系122を介 して検出器123によって検出され、その検出出力がデジタルデータとしてメモ リ124に格納される。

[0006]

半導体ウエハ121上には、チップのパターンが一定の間隔で繰り返し転写されている。半導体ウエハ121上の検査対象箇所127の画像(以下では、欠陥の検査対象となる画像ということで、欠陥画像という)を検出し、デジタルデータとしてメモリ124に格納した後、隣接するチップの同じパターンの箇所128の画像を参照画像として検出し、メモリ25に格納する。メモリ124,125に記憶した欠陥画像127と参照画像128とを比較器126で比較して欠陥を抽出し、出力する。

[0007]

以上では、参照画像として、隣接するチップの同じ個所の画像を検出して用いる場合であったが、メモリなどの繰り返しパターン部(以下、セル部という)を検査する場合には、繰り返し周期分ずらした画像を用いてもよい。通常、セル部では、物理的に離れた隣接チップの同一個所と比較するよりも、繰り返し単位を1周期分ずらした領域と比較した方が高感度の検査が可能とされる。その理由は、参照画像と欠陥画像との差画像において、正常部の輝度分布は物理的に近い方が小さい傾向にあり、従って、画像の欠陥部と正常部との信号強度の差が大きくなるからである。これは、パターンの形状ずれが物理的に近い方が小さいこと、あるいは表面膜によって生じる干渉光強度の差が物理的に近い方が小さいことなどから説明される。

[0008]

通常、繰り返しパターン部で繰り返し周期の1周期分ずらした画像を参照画像とする方法をセル比較方式といい、隣接チップの同一個所の検出画像を参照画像とする方法をダイ比較方式という。

[0009]

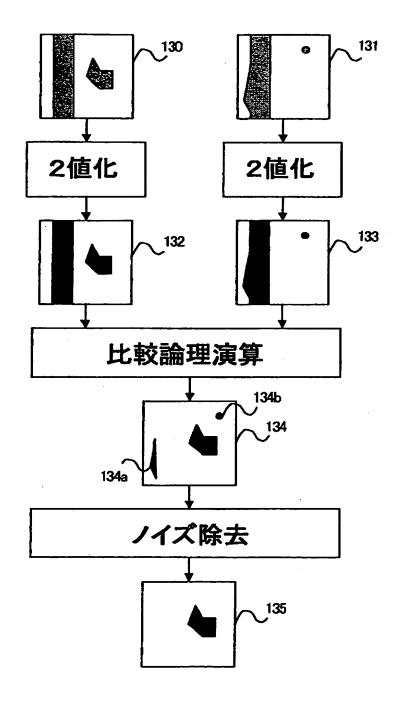

図23は図22における比較器126における比較演算についての説明図であって、130は欠陥画像、131は参照画像である。

[0010]

同図において、欠陥画像130と参照画像131とを夫々2値化、即ち、画像の輝度値が一定値(= 2値化しきい値)より大きいか、小さいかによって白黒に色分けする処理を行なって得られた2値画像132,133を比較論理演算し、その比較結果134を得る。この比較結果134中には、欠陥のみならず、欠陥画像130と参照画像131との中のパターン形状のばらつきに起因する成分134aやノイズに起因する成分134bが生じている。通常、このような欠陥領域以外の成分の検出は、虚報の原因となるため、ノイズ除去処理を行なう。ノイズ除去は、例えば、2値化画像中で径が一定値(以下、ノイズ除去しきい値)以下の場合、ノイズとみなして除去することによって実現できる。ノイズ除去処理の結果、処理結果135の如く欠陥のみが抽出される。

## [0011]

先に述べたように、ダイ比較方式では、セル比較方式よりもノイズが発生し易いため、ノイズ除去しきい値をセル比較方式よりも大きくする必要がある。ノイズ除去しきい値よりも小さな欠陥は検出できないことを意味する。

## [0012]

以上の説明において、上記の2値化しきい値やノイズ除去しきい値などは検査 パラメータ(検査条件)と呼ばれる。以下、この検査パラメータの設定について 説明する。

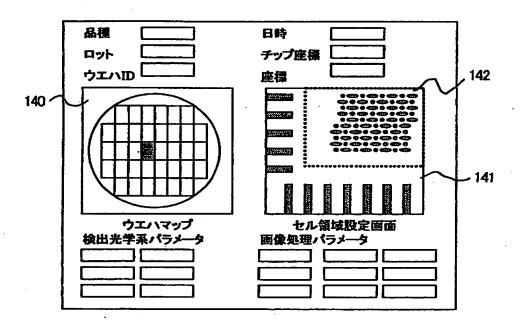

図24は典型的な検査パラメータの設定画面の一例を示す図である。

#### [0013]

同図において、検査パラメータ設定画面には、検査対象のチップを明示したウエハマップ140やこの検査対象のチップを拡大して表示するセル領域設定画面141で破線で囲むようにしてセル領域(セル部)142を選択することにより、非セル領域とは異なる検査パラメータを用いて検査を行なうことができる。即ち、セル領域142を選択した上で、このセル領域142における検出光学系パラメータや画像処理パラメータなどの各種の検査パラメータをGUI上から直接入力し、引き続き、セル領域以外の非セル領域の検査パラメータを同様にGUI上から入力する。セル領域142では、ノイズ除去しきい値を非セル部より小さく設定することにより、

非セル部よりも高感度の検査を行なうことができる。

[0014]

次に、セル領域の設定手順について説明する。

[0015]

セル領域設定画面141上でカーソルをセル領域142とする領域の外周部の所望の位置におき、マウスをクリックしてその位置をセル領域142の頂点として指定し、各頂点毎にこの指定する動作を繰り返すことにより、セル領域142の頂点群を指定し、セル領域142を設定する。この方法では、チップ領域内に10個所以上に分散して配置されている場合もあり、各セル領域に対して逐一設定する必要がある。

[0016]

次に、第2の従来技術例として、電子線式の欠陥レビュー装置について説明する。

[0017]

第1の技術例として先に説明したパターン検査装置では、欠陥の発生状況のわかっていないウエハを対象とするのに対し、欠陥レビュー装置では、パターン検査装置によって欠陥位置が既に分かっているウエハを対象として、欠陥のさらなる詳細な観察を目的として、欠陥位置の画像を再度検出するものである。

[0018]

即ち、まず、上記のようなパターン検査装置によってウエハを検査し、欠陥位置を検出する。パターン検査装置の出力情報は、ウエハ上の欠陥位置やサイズの 概略などの簡単な欠陥に関する情報からなっている。

[0019]

通常、パターン検査装置における欠陥検出においては、検査時間を短縮するために、欠陥のサイズに対して、その詳細が観察できるほどには充分に高い倍率では画像を検出しない。

[0020]

欠陥レビュー装置は、パターン検査装置の出力情報を入力として、ウエハ上の 欠陥位置の画像とこの画像に対応する参照画像とを欠陥の詳細が観察できるほど 充分高い倍率で撮像する。撮像倍率は事前にユーザが設定する検査パラメータの 1つであり、全ての欠陥に対して事前に設定した特定の倍率で画像を撮像する。

[0021]

次に、欠陥検査装置におけるパラメータ設定の手順についてを説明する。

[0022]

かかるパラメータは、画像の撮像条件を設定するパラメータ(以下、画像検出パラメータという)と、画像処理条件を設定するパラメータ(以下、画像処理パラメータという)に大別される。画像検出パラメータは、適正な画像を検出するためのパラメータであり、例えば、電子線式の外観検査装置であれば、検出倍率や非点収差の補正条件、プローブ電流値、加速電圧、ゲイン、オフセット補正量、画像の加算回数などがこれに相当する。また、画像処理パラメータは、検出した画像を適正に処理するために設定が必要なパラメータである。例えば、検出した画像から欠陥部のみを2値化抽出するための2値化しきい値や、欠陥とは関係ない微小な面積の領域をノイズとして除去するノイズ除去しきい値、エッジにおける感度低下パラメータなどがこれに相当する。

[0023]

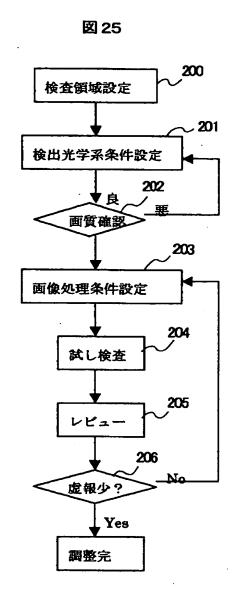

検査パラメータ設定手順の典型的なフローチャートを図25により説明する。

[0024]

始めに、検査対象領域を設定する(ステップ200)。検査対象領域は、半導体ウエーハ面上のチップレイアウトやチップサイズなどのデータを入力することにより、指定する。さらに、一部の欠陥検査装置では、セル領域、非セル領域など、チップ内を複数の部分検査領域に分割設定する。

[0025]

検査対象領域は、以下の手順で設定する。分割される上記の部分検査領域は、 例えば、矩形状とする。オペレータは、矩形の部分検査領域を指定するために、 試料面上を撮像して得られた画像を操作画面上に表示させながら、かかる矩形の 頂点が視野内に入るように、半導体ウエハが搭載されたステージを移動させ、操 作画面上で、カーソルなどにより、矩形の頂点位置を指定する。矩形の各頂点に 対して同様の操作をおこなうことにより、矩形上の部分検査領域を設定すること ができる。部分検査領域が複数ある場合には、以上の矩形領域の設定操作をさら に繰り返し行なう必要がある。

## [0026]

次に、画像検出パラメータを仮設定し(ステップ201)、検査対象領域から 適当に選択した位置で画像を検出し、オペレータの目視によって画質良否を判断 する(ステップ202)。ここで、画質が不良であれば、画像検出パラメータを 再設定する。

## [0027]

次に、設定した画像検出パラメータにおいて、画像処理パラメータを仮設定し(ステップ203)、仮検査を実行する(ステップ204)。この検査実行後、検出欠陥位置を確認し、画像処理パラメータの設定状態を検証する(ステップ205)。仮に、虚報が想定以上多数で存在している場合には(ステップ206)、感度が高すぎるから、感度を下げる。また、例えば、必要以上に微細な欠陥を検出する場合には、ノイズ除去サイズを大きくする。あるいは、例えば、x,y方向の一方にのみ細長い虚報を検出する場合には、xもしくはy方向の一方のノイズ除去サイズを大きくすることが考えられる。予め半導体ウエハ上に検出すべき欠陥を標準欠陥として指定しておき、これら標準欠陥が検出される範囲で検出感度を落とすように、パラメータを調整する場合もある。逆に、検出欠陥数が少なすぎたり、標準欠陥を検出できなかったりした場合には、感度を上げる。

#### [0028]

以上の画像処理パラメータの再設定や仮検査再実行、検査結果再確認の各操作を、虚報が一定件数以下になる、あるいは標準欠陥が見つかる範囲で虚報が一定件数以下になるなど、パラメータ調整完了と判断される所望の条件を満足するまで繰り返し実行する。

## [0029]

## 【発明が解決しようとする課題】

上記従来技術として説明したように、セル比較方式とダイ比較方式とのいずれ を実行するかを含めて、検査パラメータ一般について被検査対象領域を多数の部 分検査領域に分割し、各部分検査領域毎に異なる検査パラメータを設定しようと しても、各部分検査領域の設定は人手に頼らざるを得ず、効率的に行なうことができない。実質的に検査パラメータが異なる多数の部分検査領域に分割し、部分 検査領域毎に異なる検査パラメータで検査することは実質的に不可能となっている。これは以下の点で不利である。

[0030]

まず、第1に、検出欠陥数の爆発を回避することができない。パターンの密度によって、致命的な欠陥のサイズは異なる。即ち、パターン密度が高いところでは、より小さなサイズの欠陥までも確実に検出できることが重要である。しかるに、欠陥検出感度をパターンが密な領域で適正となる程度に充分高く設定した場合、これを被検査領域全面に適用すると、欠陥検出数が数1000個以上に及んでしまい、管理が困難になってくる。また、パターンが粗な部分では、必要以上に検出感度を高く設定せず、適切な低さに設定することができれば、検出欠陥数を減らすことができ、致命欠陥数の把握など管理の上で有利となる。

[0031]

第2に、検査パラメータを場所毎に最適化することができない。検査パラメータには、先に説明した致命性に関連するパラメータが例に挙げることができる。

この他にも、画像検出条件に関連するパラメータについて、上記第2の従来技術例として紹介した欠陥レビュー装置を例に説明すると、先に述べたように、パターンの疎密によって管理上検出が最も重要な欠陥サイズが決まる。画像を検出する際の撮像倍率は、この欠陥サイズの欠陥が撮像画像サイズに対して適切な程度に設定しなくてはならない。しかし、現状では、一定の撮像倍率で画像を検出しているので、欠陥のサイズに対して、倍率が過大もしくは過小になる場合がしばしば生じる。

[0032]

また、図25で説明した従来の手順では、被検査領域の設定に多大な労力を要するという問題点がある。従来では、チップ内をセル領域と非セル領域など複数の部分領域に分割するに際し、分割数が多い場合には、実質的に被検査領域の設定が困難になってしまう。さらには、分割した各部分検査領域毎にパラメータの設定及び調整を行なう労力が膨大になる、という問題もある。

[0033]

さらに、チップ上の特定の領域における虚報の多発を回避できる。被検査領域を一様な感度で検査した場合、チップ上の特定の領域で虚報が多発する場合がある。例えば、チップ上の特定のパターンの形状精度が悪い場合や特定のパターンにおいて、検出系の特性によって虚報を生じてしまう場合がこれに当たる。かかる虚報は、虚報多発領域を他の検査領域から分離した検査領域として設定し、この設定領域において感度を下げるか、あるいは検査しないことによって回避できる。被検査領域の大きさはチップと同程度のスケール設定した方が望ましい場合もあるし、あるいは、特定のパターンに対して検出感度を下げるように、パターンと同スケールの微細な領域に設定した方が望ましい場合もある。

[0034]

以上のように、被検査領域を複数の部分検査領域に分割し、これら部分検査領域毎に異なる検査パラメータを設定して検査すること、あるいは、被検査領域中の特定のパターンに対して検査パラメータを設定して検査することが重要であるにもかかわらず、従来では、その実現に膨大な労力を要するか、あるいは事実上実現できないという問題があった。

[0035]

本発明の目的は、かかる問題を解消し、被検査領域での部分検査領域の設定の 効率化を図り、各部分検査領域に設定する検査パラメータの最適化を容易に可能 とした電子回路パターンの欠陥検査管理システム,電子回路パターンの欠陥検査 システム及び装置を提供することにある。

[0036]

【課題を解決するための手段】

上記目的を達成するために、本発明は、被検査対象領域を検査条件が異なる少なくとも2個以上の部分検査領域に分割する検査領域設定手段と、該検査領域設定手段によって設定された各部分検査領域に対して、検査条件を設定する検査条件設定手段と、該検査領域設定手段によって設定された各部分検査領域に対して、該検査条件設定手段によって設定した検査条件で検査を実行する検査実行手段とを有する構成をなすものである。

[0037]

そして、検査領域設定手段は、レイアウトパターンに基づいて、被検査対象領域を複数の部分検査領域に分割する構成とするものである。

[0038]

また、上記目的を達成するために、本発明は、レイアウトデータに基づいて被検査領域を、例えば、機能ブロック毎、あるいは、配線密度がほぼ同程度のブロック毎、あるいは、致命度の異なるブロック毎に分割する検査領域設定手段と、この検査領域設定手段によって設定された各部分検査領域に対して検査条件を設定する検査条件設定手段と、この検査領域設定手段によって設定した各部分検査領域を検査条件設定手段によって設定した検査条件で検査を実行する検査実行手段とを有する構成とし、これにより、被検査領域を複数の部分検査領域に分割する労力を大幅に低減できる。

[0039]

さらに、レイアウトデータに基づいて、被検査領域を検査条件が異なる複数の部分検査領域に分割する検査領域設定手段と、この検査領域設定手段によって設定された各部分検査領域に対し、検査条件の初期値や検査条件の調整ルール並びに検査条件の収束条件を設定する検査条件設定手段と、検査対象個所の画像を検出する画像検出手段と、各部分検査領域において、この画像検出手段によって検出した画像を、検査領域設定手段により、部分検査領域毎の画像に分割して、検査条件の初期値を用いて処理し、各部分検査領域毎に欠陥を検知する検査実行手段と、欠陥個所の画像を記憶する画像記憶手段とを有する構成とする。これにより、分割した部分検査領域毎に検査パラメータを設定する労力が大幅に低減される。

[0040]

- 【発明の実施の形態】

以下、本発明の実施形態を図面により説明する。

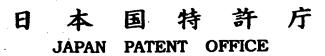

図1は本発明による電子回路パターンの欠陥検査管理システムの第1の実施形態を示す構成図であって、1はパターン検査装置、2は設計情報サーバ、3はLANなどのネットワークである。

# [0041]

同図において、パターン検査装置1はネットワーク3を介して設計情報サーバ2と接続されており、設計情報サーバ2との間でデータの授受が可能となっている。設計情報サーバ2には、パターン検査装置1で検査する半導体ウェハのレイアウトデータが格納されており、パターン検査装置1は、このレイアウトデータを基に、半導体ウェハでのチップの検査対象領域をセル部と非セル部とに分割し、夫々毎に検査パラメータ(検査条件)を設定するものである。

# [0042]

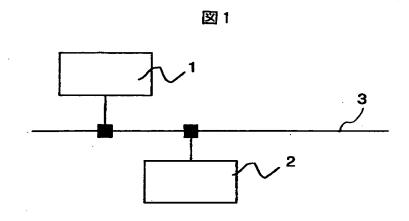

レイアウトデータは、半導体ウェハのマスク製作などに用いられる汎用的なデータであって、各層における配線配置を配線の端点の座標や幅などの数値から成るベクトルデータである。レイアウトデータを画像に展開したものをレイアウトパターンといい、その一例を図2に示す。かかるレイアウトパターンは、レイアウトデータから容易に合成することができる。

# [0043]

以下では、レイアウトデータに基づいて、検査対象領域をパターンの稠密度が 異なる複数の部分検査領域に分割する手法について説明する。

#### [0044]

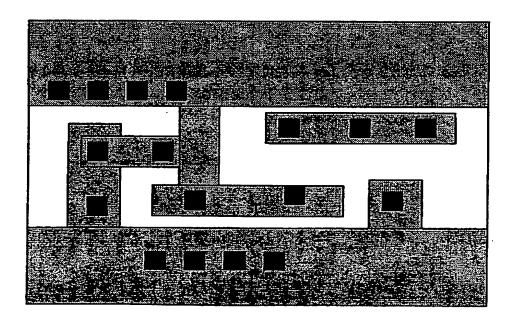

最も単純な手法としては、検査対象領域をレイアウトデータに基づいて、部分 検査領域としてのセル部と非セル部に分割する方法が考えられる。レイアウトデータは、各機能ブロック毎にモジュール化された階層構造を有している。図3に示すように、システムLSIでは、チップ内に複数の設計モジュールがあり、セル部が分散配置されていることもある。セル部を含め、各モジュールの領域をレイアウトデータから抽出することができる。即ち、一般に、検査対象領域データSは、モジュール毎に記述されたレイアウトデータに従って、次のような部分検査領域データに分割することができる。

#### [0045]

次に、分割した各部分検査領域毎に検査条件を設定する方法について説明する

# [0046]

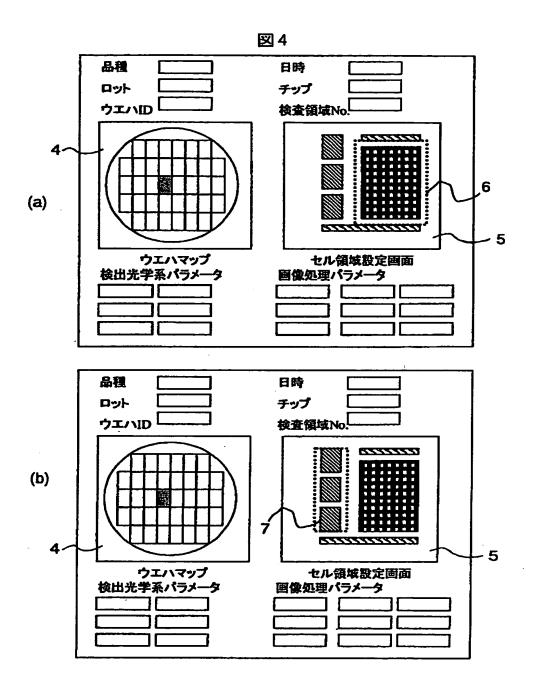

図4は検査条件設定のための検査パラメータ設定画面の一具体例を示す図である。

## [0047]

図4において、検査パラメータ設定画面には、図24に示した従来の検査パラメータ設定画面と同様、検査対象のチップを明示したウエハマップ4やこの検査対象のチップを拡大して表示するセル領域設定画面5などが表示される。図4(a)はセル領域設定画面5での一方の部分検査領域6に対するパラメータ設定画面を、図4(b)は同じ検査対象領域のセル領域設定画面5での他方の部分検査領域7に対するパラメータ設定画面を夫々示しており、夫々毎に検査パラメータが入力設定される。図4(a),(b)のいずれのパラメータ設定画面でも、検出画像にレイアウトデータに基づいて設定される各部分検査領域6,7を表わす枠がオーバレイして表示されている。

## [0048]

このようにして、パターン検査装置1(図14)では、部分検査領域6が図4 (a)に示すパラメータ設定画面で入力された検査パラメータを基に検査が行なわれ、部分検査領域7が図4(b)に示すパラメータ設定画面で入力された検査パラメータを基に検査が行なわれる。

#### [0049]

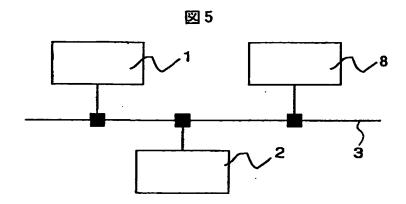

図5は本発明による電子回路パターンの欠陥検査管理システムの第2の実施形態を示す構成図であって、8は欠陥レビュー装置であり、図1に対応する部分には同一符号をつけて重複する説明を省略する。

#### [0050]

同図において、この第2の実施形態では、図1に示した構成に加え、欠陥レビュー装置8がLAN3に接続されており、パターン検査装置1や設計情報サーバ2との間でデータの授受が可能となっている。また、設計情報サーバ2は、検査対象となる製品の各品種や工程毎に設計情報を記憶している。

## [0051]

欠陥レビュー装置 8 は、ウエハ上での欠陥位置が既に分かっているウエハを対象として、欠陥のさらなる詳細な観察を目的として、欠陥位置の画像を再度検出

するものである。即ち、パターン検査装置1によって検出された欠陥位置が、検査結果情報として、欠陥レビュー装置8に転送される。この検査結果情報はテキスト情報であり、欠陥のID (Identification) や欠陥のX, Y座標から成るものである。

[0052]

欠陥レビュー装置 8 は、検査結果情報中に記録された各欠陥位置の画像を取得する。そして、各欠陥の画像を取得する際、撮像倍率などの検査パラメータを欠陥の位置する領域の特性(セル/非セルやパターン密度など)に応じて決定する。このために、画像検出に先立って、設計情報サーバ2からレイアウトデータを取得する。ユーザは欠陥レビュー装置 8 の操作画面上で検査対象品の品種や工程の情報を入力する。欠陥レビュー装置 8 は入力された対象となる品種や工程のレイアウトデータを設計情報サーバ2から検索し、取得する。そして、取得したレイアウトデータに基づいて、部分検査領域データを生成する。ここで、部分検査領域データとは、第1の実施の形態で言及したものと全く同様とする。

[0053]

次に、かかる部分検査領域データに基づいて、2種類の検査パラメータを部分 検査領域毎に変更する方法を説明する。

[0054]

変更する2種類の検査パラメータは、画像検出モードと撮像倍率である。これ ら検査パラメータの意味並びに場所毎に変更する目的について説明する。

[0055]

画像検出モードは、参照画像を検出するか否かを指定するパラメータである。

[0056]

セル部は、同一のパターンの繰り返しからなるので、事前にセル部の画像を撮像して記憶しておけば、欠陥 I D毎に毎回参照画像を検出する必要はなく、記憶した画像を繰り返し参照画像として使用することができる。参照画像を新たに検出する場合には、半導体ウェハを搭載したステージを所望の位置に移動させ、撮像領域に電子線を照射して画像を検出するステップを経る必要があるために、記憶装置に記憶した参照画像を繰り返し流用する場合に比べて、多くの時間を要す

ることになる。従って、参照画像を流用するモードにおいては、検査時間を大幅 に短縮することができるために有利である。

[0057]

以下では、参照画像を記憶し、流用するモードを『参照画像レスモード』といい、参照画像を欠陥ID毎に毎回検出するモードを『参照画像検出モード』ということにする。検査対象領域中のセル領域に対しては『参照画像レスモード』を、非セル領域に対しては『参照画像検出モード』を夫々設定することにより、検査時間を大幅に短縮することができる。

[0058]

撮像倍率は、画像を検出する倍率である。レビュー作業は、欠陥の詳細な観察が目的であるから、欠陥の大きさに対して適正な撮像倍率を設定しなければならない。但し、欠陥の大きさに関する情報がない場合には、任意の大きさの欠陥に対して適正な倍率を設定することはできないので、現実的には、最も観察が重要な欠陥のサイズに対して適正となるように撮像倍率を設定する。最も観察が重要なサイズは、配線の平均的な間隔から定まる致命性判定基準サイズに基づいて決定することができる。

[0059]

次に、本発明による電子回路パターンの欠陥検査管理システムの第3の実施形態について説明する。

[0060]

この第3の実施形態も、図5に示す構成をなすものであるが、先に説明した第1,第2の実施形態に対して、さらに、部分検査領域のフレキシブルな調整を可能とするものである。上記第1,第2の実施形態では、部分検査領域の設定をレイアウトデータに基づいて完全に自動的に行なうために、部分検査領域のフレキシブルな調整が必ずしも可能とはいえない。この第3の実施形態では、パターン検査装置で検出した欠陥位置を欠陥レビュー装置によってレビューし、そのレビュー結果を、さらに、パターン検査装置の検査パラメータ設定にフィードバックするものである。

[0061]

即ち、図5において、パターン検査装置1によって検出された欠陥位置は検査結果情報として、欠陥レビュー装置8に転送される。欠陥レビュー装置8はレビューを行ない、各欠陥に欠陥の種類などの夫々の欠陥に関する情報を付与したレビュー結果情報を生成する。パターン検査装置1は、必要に応じて、欠陥レビュー装置8からレビュー結果情報を読み出すことができる。

# [0062]

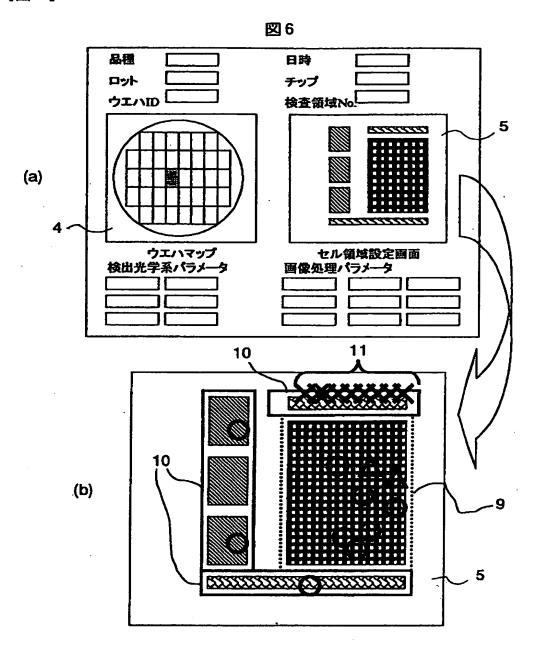

図6(a)はこの第3の実施形態でのレビュー結果情報を取得したパターン検出装置1におけるパラメータ設定画面を示す図であって、図4に対応する部分には同一符号をつけている。また、図6(b)は図6(a)におけるセル領域設定画面5を拡大して示す図であり、9はセル部、10は非セル部、11は欠陥群である。

# [0063]

同図(a)に示すパラメータ設定画面では、検査対象とするチップが明示されたウェハマップ4と、このチップを拡大して示すセル領域設定画面5などが表示され、このセル領域設定画面5では、図6(b)に示すように、部分検査領域の設定状態やレイアウトデータ、検出画像、レビュー結果情報の少なくとも1個以上が並列して表示され、もしくはこれらがオーバレイ表示される。ここで、オーバレイ表示とは、複数のマップを半透明化して重ね合わせ表示するものである。オーバレイ表示により、マップ間の重なり具合を容易に観察することができる。

## [0064]

図6(b)において、太破線で囲んで示すセル部9では、その部分検査領域の設定状態と検出画像とレビュー結果情報とがオーバレイ表示されている。部分検査領域であるセル部9を規定する太破線の枠と部分検査領域である非セル部10を規定する太実線の枠とは設計情報サーバ2(図5)に蓄積されているレイアウトデータに基づくものであって、セル領域設定画面5にセル部9と非セル部10の画像にオーバレイ表示される。これらセル部9と非セル部10とには、異なる検査パラメータがセットされる。検査パラメータは、セル部9では、検出感度大に設定され、非セル部10では、検出感度小に設定される。〇、△、×などの記号はセル部9及び非セル部10にオーバレイ表示されるレビュー結果情報を示し

ている。ここでは、かかるレビュー結果情報は、一例として、欠陥の種類に対応 しており、〇は異物、△はへこみ、×は虚報を夫々示している。これら欠陥の発 生位置がかかる記号の表示位置となる。

## [0065]

ユーザは、かかるセル領域設定画面 5 を観察することにより、検出した欠陥数が多すぎないか、また、不自然に少なくないかなど、即ち、検出感度が妥当か否かを確認することができる。

#### [0066]

ここで、部分検査領域はユーザが自由に編集できるものとする。具体的には、 新たな部分検査領域の追加や既存の部分検査領域の削除, 既存の部分検査領域へ の部分的な領域の追加,削除が可能である。

## [0067]

また、検査対象領域内の特定箇所に虚報が集中して発生することがある。これには、プロセスに起因して特定の箇所でパターンの形状精度が不安定になる、あるいは特定の箇所で膜厚のばらつきが大きくなって干渉光強度のばらつきが大きくなるなどの原因が考えられる。図6(b)では、1つの非セル部10で示す欠陥群11がこれに対応している。ユーザはセル領域設定画面5を観察して、不自然に欠陥が特定箇所に集中している、もしくは直線上に並んでいる、といったような欠陥の分布に特異なパターンが認められる場合、欠陥の発生箇所を拡大表示することにより、虚報か否か確認することができる。画像を拡大表示して確認し、検出不要と判断される場合には、虚報の集中発生領域周辺に新たに部分検査領域を設定し直し、その部分検査領域内での検査感度を下げることにより、検出不要な欠陥の数を低減することができる。

## [0068]

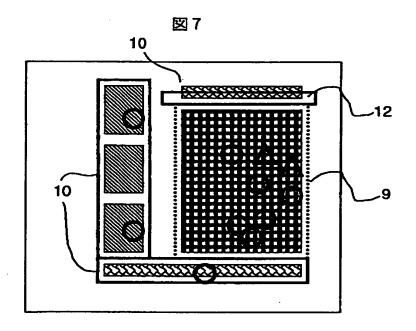

図7は図6(b)に示すセル領域設定画面5で以上のように設定した部分検査 領域(×で示す虚報が不自然に発生した非セル部10の部分検査領域)を再編集 した結果を示す図であって、×で示す虚報を除いた再編集後のセル領域設定画面 5に上記の検査結果やレビュー結果情報をオーバレイ表示している。部分検査領 域12は、×で示す虚報が検査領域から除かれることにより、図6に示す部分検 査領域に対して縮小されている。この結果、図6における虚報群11の出力が抑 制されることになる。

## [0069]

次に、レイアウトデータに基づいて検査領域をパターンの粗密の程度が異なる 複数の領域に自動分割し、分割領域毎の検査パラメータ最適化を容易化する本発 明による電子回路パターンの欠陥検査装置及び検査システムの実施形態について 説明する。

# [0070]

以下に説明する実施形態に用いるレイアウトデータも、上記のように、半導体ウエハのマスク製作などに用いられる汎用的なデータであり、各層における配線の配置を配線の端点の座標や幅などの数値によって記述したベクトルデータである。レイアウトデータを画像に展開したデータをレイアウトパターンという。レイアウトパターンをレイアウトデータから合成する技術は、レイアウト設計の検証などで広く用いられている。

## [0071]

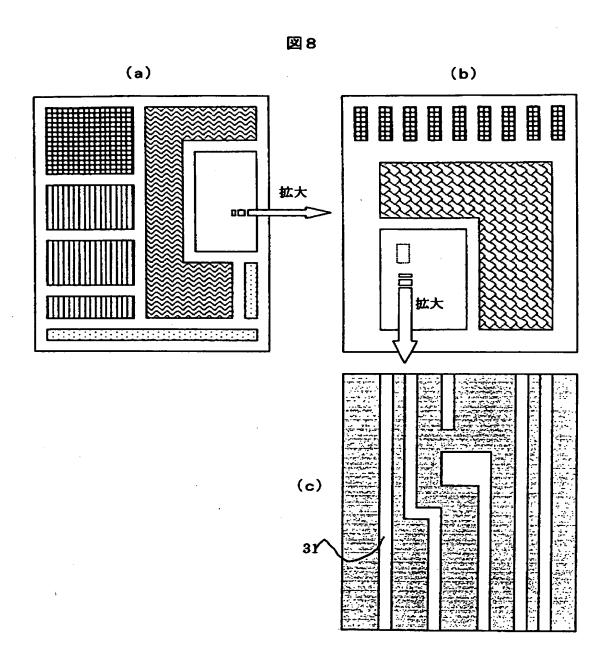

図8はかかるレイアウトパターンの一具体例を示すものであって、図8(b)は図8(a)に示すパターンの一部を拡大したもの、図8(c)は図8(b)に示すパターンの一部を拡大したものである。

#### [0072]

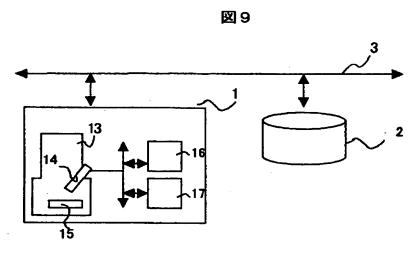

図9は本発明による電子回路パターンの欠陥検査装置及びシステムの第1の実施形態を示す構成図であって、13は走査型電子顕微鏡、14は画像検出器、15は半導体ウエーハ、16は記憶装置、17は画像処理コンピュータであり、図1に対応する部分には同一の符号を付けている。

## [0073]

同図において、パターン検査装置1は走査型電子顕微鏡(以下、単に電子顕微鏡という)13を備えており、電子顕微鏡13の筐体内に載置された被検査対象の半導体ウエーハ15の画像を画像検出器14で検出する。検出した画像は、バスを介して、画像処理コンピュータ17に転送される。画像処理コンピュータ17は、この検出画像を処理して画像の欠陥の検出や欠陥の分類処理を行なう。ま

た、検出画像などは、記憶装置16に記憶することもできる。レイアウトデータ を蓄積している設計情報サーバ2は、LANやDATなどの記憶媒体を介して、 パターン検査装置1と互いにデータの授受が可能な構成となっている。

## [0074]

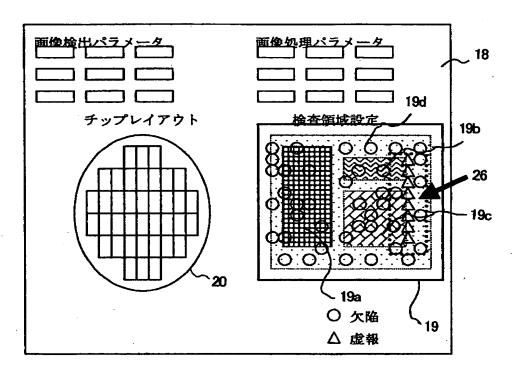

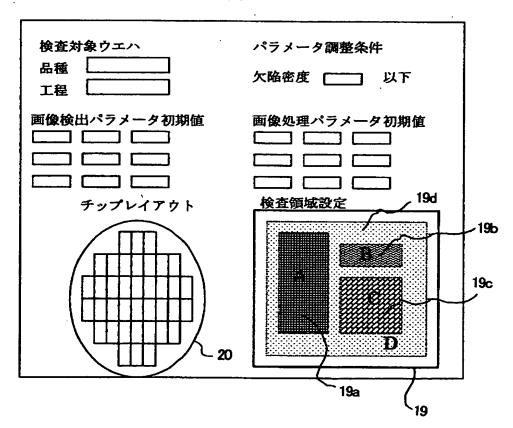

画像処理コンピュータ17は、このパターン欠陥検査システムの制御を指令するためのユーザインターフェースを備えている。図10は画像処理コンピュータ17のユーザインターフェースの一部である検査パラメータ設定画面18の一具体例を示す図である。

# [0075]

ユーザは、この検査パラメータ設定画面18を介して、検査対象の半導体ウエーハの品種、工程や画像検出パラメータ、画像処理パラメータ、検査領域の設定を行なう。ユーザが検査対象の半導体ウエーハの品種を入力すると、画像処理コンピュータ17は、設計情報サーバ12から対象品種のレイアウトデータを記憶装置16に転送する。また、同一品種の別ウエーハを既に検査したことがあり、そのレイアウトパターンが記憶装置16に記憶されている場合には、記憶装置16に再転送する必要はない。

## [0076]

詳細は後述するが、画像処理コンピュータ17は、このレイアウトデータに基づいて、検査対象領域をパターン密度の異なる複数の領域に自動分割して、ユーザに分割領域の確認、修正を促し、さらに、これら分割領域毎に検査パラメータの設定を促す。

#### [0077]

図10に示す検査パラメータ設定画面18には、被検査領域19の自動分割結果が示されており、ここでは、この被検査領域19はAの部分領域19aとBの部分領域19bとCの部分領域19cとDの部分領域19dとに分割されているものとしている。被検査領域19には、チップ全体のレイアウトパターンを表示すると同時に、レイアウトデータに基づいて、画像処理コンピュータ17が算出した領域分割の算出結果を表示している。点線で示す部分領域19a~19dは、この領域分割の算出結果である。各部分領域19a~19dは、夫々の領域内

において、同程度のパターン密度を持っており、画面中には、分割された各部分 領域19a~19d毎の属性、例えば、平均ライン間隔などを表示する。ユーザ は、画像処理コンピュータ17が算出したかかる領域分割に対して、被検査領域 19の設定画面上で必要に応じて修正することもできる。

[0078]

次に、レイアウトデータに基づいて、被検査領域19をパターンの密度が異なる複数の領域に自動分割する方法について説明する。

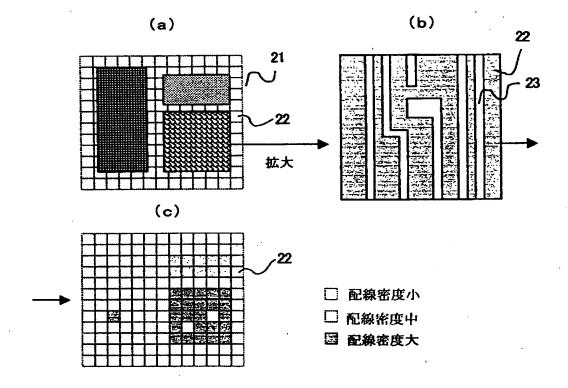

図11はかかる自動分割方法の第1の具体例を示す図である。

[0079]

この具体例は、チップレイアウトを格子状に分割し、各格子における配線面積の密度が同程度の領域をグループ化する方法であって、まず、図11(a)に示すように、チップ領域(被検査領域19)21を格子状に分割する。図11(b)はかかる1つの格子22内の配線23のレイアウトパターンを拡大して示すものであって、このレイアウトパターンでは、図を見易くするために、格子22内に数本の配線23しか含まれていないものとしているが、実際には、この格子22をより大きい面積の矩形領域に設定した方が、計算時間上、望ましい。

[0080]

次いで、格子毎に、配線の占める面積の割合を算出する。即ち、

配線密度=配線の面積/格子の面積

を算出する。配線密度は格子22内に含まれる配線23の面積から求めることができる。あるいは、レイアウトデータをレイアウトパターンに展開することなく、レイアウトデータに記述されたパターンの分布範囲から直接、配線密度を算出することもできる。図11(c)は各格子22毎に算出した配線密度の大きさに応じて格子22を色づけした様子を示している(ここでは、都合上濃淡で示している。)。白いほど配線密度が低く、黒いほど配線密度が高い。

[0081]

次いで、各格子22の配線密度の大きさに従って、その格子22にラベルを与える。例えば、配線密度の大、小を判定するためのしきい値(ThH,ThL)を事前に組み込んでおき、これを格子22の配線密度Dと比較し、

- ・D>ThHならば、ラベル『配線密度大』

- ・ThH>D>ThLならば、ラベル『配線密度中』

- ・ThL>Dならば、ラベル『配線密度小』

とする。検査条件設定時には、各ラベル毎に検査パラメータを設定する。これにより、各格子22を検査する際には、各格子22に付されたラベルに対応する検査パラメータにより、検査を行なう。例えば、ラベル『配線密度大』が付された格子22に対しては、ラベル『配線密度大』に対して設定された検査パラメータにより、検査を実行する。

# [0082]

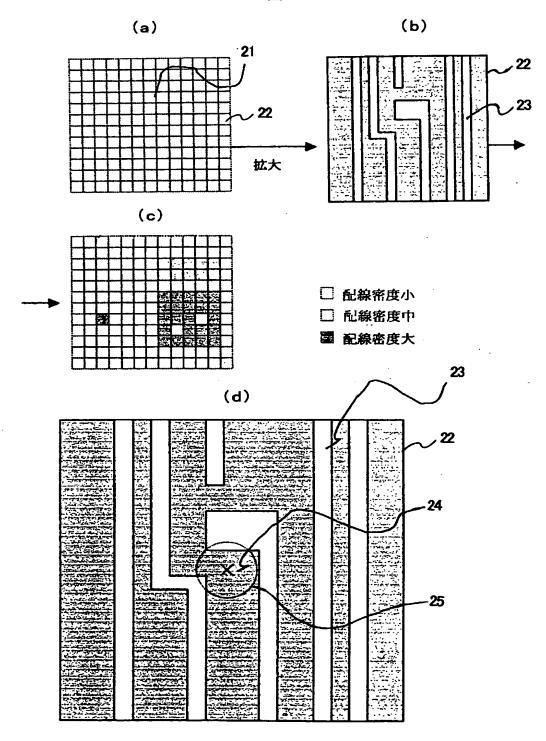

また、被検査領域19(図10)を配線密度が同程度の領域に分割するため他の方法として、モンテカルロシミュレーションによる方法がある。これを図12を用いて説明する。

## [0083]

先の説明と同様に、まず、図12(a)に示すように、被検査領域21を格子 状に分割する。図12(b)は1つの格子22内での配線23のレイアウトパタ ーンを拡大して示す。そして、各格子22内で以下の処理を行なう。

## [0084]

即ち、図12(b)を拡大して示す図12(d)において、格子22内のランダムな位置に配線密度算出用の点24を発生させる。次いで、この配線密度算出点24を中心とした仮想的な半径rの円25を設定し、この仮想円25の内側に配線23のパターンが含まれるような、半径rの最小値r<sub>min</sub>を求める。この最小値r<sub>min</sub>は配線密度算出点24から最も近い配線23のエッジまでの距離を意味する。最小値r<sub>min</sub>が大きいほど、配線密度算出点24近傍での配線23のパターンが疎であり、逆に、最小値r<sub>min</sub>が小さいほど、配線密度算出点24近傍での配線23のパターンが密であると言える。

## [0085]

このようにして、格子22内で複数回、配線密度算出用の配線密度算出点24をランダムな位置に発生させ、これを中心とする仮想円25の最小半径 r<sub>min</sub>の平均値を求める。発生回数が大きいほど、その格子22内の配線23のパターン

の平均的な粗密が反映した値となる。

[0086]

このようにして、各格子22における配線23のパターンの粗密を算出することができる。その計算結果を図12(c)に示す。かかるモンテカルロシミュレーションによる方法は、計算時間の点において、先に述べた、格子22内の配線23のパターンの面積を算出する方法よりも優る。実際、面積を算出する方法では、被検査領域21の全配線パターンについて面積を算出することが必要であるが、モンテカルロシミュレーションによる方法の場合、ランダムに発生させた配線密度算出点24における計算処理のみでよいからである。

[0087]

以上述べたように、レイアウトデータに基づいて算出した被検査領域21の分割結果を、図10に示す検査パラメータ設定画面18上に示す。さらに、試し検査実行(図25のステップ204)後、図13に示すように、検査パラメータ設定画面18に欠陥のレビュー結果、即ち、欠陥の位置と種類をオーバレイ表示する。ここでは、実欠陥をシンボル「〇」で、欠陥の虚報をシンボル「△」で夫々表示するようにしている。

[0088]

ユーザは、かかる検査パラメータ設定画面18から表示された領域分割結果, 欠陥のレビュー結果並びにレイアウトデータを確認することができる。また、実 欠陥と虚報を異なるシンボルで表示しているため、例えば、矢印26で示すチップ上の特定領域で集中的に虚報が発生していることを容易に把握できる。さらに、レイアウトパターンと重ね合わせて表示(オーバレイ表示)しているため、虚報の発生位置とレイアウトとの関係を容易に把握できる。ユーザは、表示画面を観察して、特定個所で集中的に虚報が発生していることが分かると、その近傍の検査感度を下げるように、部分検査領域を新たにマニュアルで設定することができる。また、複数のチップについて、レビュー結果を重ね合わせた様子を表示してもよい。重ね合わせて表示することにより、個別チップでの欠陥発生状況からは観察されにくい現象を観察することができる。

[0089]

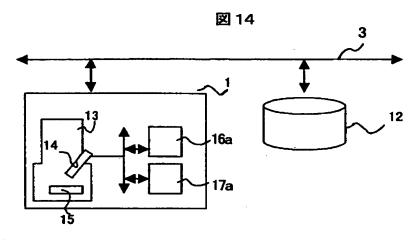

図14は本発明による電子回路パターンの欠陥検査装置及びシステムの第2の 実施形態を示す構成図であって、16aは記憶装置、17aは画像処理コンピュ ータであり、図9に対応する部分には同一の符号を付けている。

[0090]

この第2の実施形態においては、図9に示した第1の実施形態と異なり、被検査領域を、レイアウトデータに基づいて、機能ブロック(もしくは設計モジュール)毎に分割するものである。そして、分割された機能ブロック毎に検査パラメータを設定し、これを検査パラメータデータベースに登録する。これにより、他品種の半導体ウエハに対しても、機能ブロックが共通している場合、新たな検査パラメータ設定が不要となる。即ち、新品種の半導体ウエハの検査に際して、レイアウトデータに含まれる機能ブロックの検査パラメータが既に検査パラメータデータベースに登録されているか否か検索し、既に登録されている場合には、これを検査条件として設定する。

[0091]

図14において、画像処理コンピュータ17aと記憶装置16aとは夫々、図9での画像処理コンピュータ17と記憶装置16の機能に加えて、検査パラメータのデータベース機能も有している。

[0092]

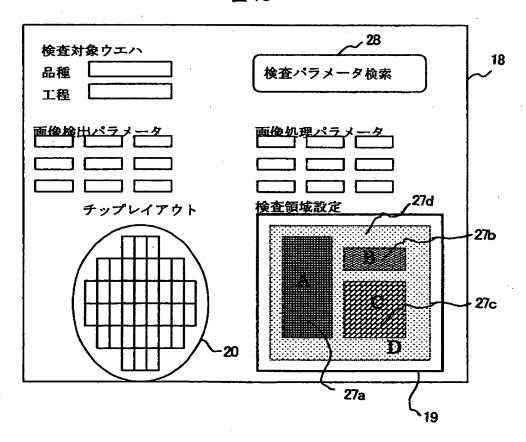

図15はこの実施形態での検査パラメータ設定画面18を示す図である。

[0093]

同図において、被検査領域19は機能ブロック27a,27b,27c,27dに分割される。ユーザは、画面18上の検査パラメータ検索ボタン28を図示しないカーソルなどを用いて操作することにより、これら機能ブロック27a~27dの検査パラメータが検査パラメータのデータベース機能を有する画像処理コンピュータ17aと記憶装置16aに登録されているか否か検索し、既に、登録されている場合には、これを流用し、登録されていない場合にのみ、新規に検査パラメータを設定登録する。

[0094]

ところで、図9に示した実施形態では、被検査領域19をパターンの粗密に応

じて分割するものとしたが、領域の致命度に応じて被検査領域を分割した方が望ましい場合もある。例えば、コンタクトホール形成工程などでは、穴の配置の粗密によって検査条件を変えるのではなく、穴とそれ以外の個所で検査条件を変えた方が望ましいことがある。このような場合には、被検査領域19の致命度の大小をレイアウトデータに基づいて求め、致命度に応じて検査条件を変更すればよい。具体的には、レイアウトデータに基づいて穴が配置された領域を求め、これを部分検査領域とすればよい。

## [0095]

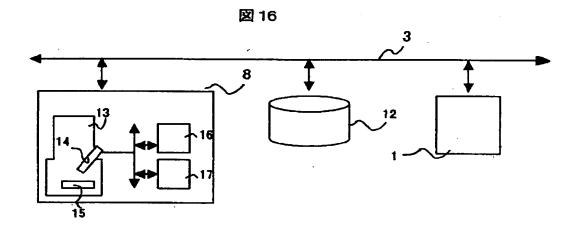

図16は本発明による電子回路パターンの欠陥検査装置及びシステムの第3の 実施形態を示す構成図であって、前出図面に対応する部分には同一の符号を付け ている。

## [0096]

同図において、この第3の実施形態においては、ネットワーク3に電子線式の 欠陥レビュー装置8も接続されている。この欠陥レビュー装置8も、図9におけるパターン検査装置1と同様、走査型電子顕微鏡13,画像検出器14,記憶装置16及び画像処理コンピュータ17を備えたものであり、パターン検査装置1による検査で欠陥位置が既に分かっている半導体ウエハ15を対象とし、欠陥の更なる詳細な観察を目的として、欠陥位置の画像を再度検出するものである。即ち、パターン検査装置1は図9,図14におけるパターン検査装置1と同様のものであって、このパターン検査装置1によって検出された半導体ウエハ15での欠陥位置は、検査結果情報として、レビュー装置8に転送される。ここで、検査結果情報はテキスト情報であり、欠陥のIDや欠陥のX,Y座標情報からなるものとする。

# [0097]

欠陥レビュー装置 8 は、検査結果情報中に記録された各欠陥位置の画像を取得し、また、各欠陥の画像を取得する際、撮像倍率などの検査パラメータを欠陥の位置する領域の特性(セル/非セルやパターン密度など)に応じて決定する。このために、画像検出に先だって、設計情報サーバ12からレイアウトデータが転送される。ユーザは、欠陥レビュー装置 8 の操作画面上で検査対象品の品種,工

程を入力するし、欠陥レビュー装置8は、対象となる品種,工程のレイアウトデータを設計情報サーバ12から検索する。

[0098]

欠陥レビュー装置8は、転送したレイアウトデータに基づいて、被検査領域を セル部と非セル部に分割する。

[0099]

この実施形態では、セル部と非セル部とで検査パラメータ(画像検出モード) を変更する。これら検査パラメータの意味並びに場所毎に変更する目的について 説明する。

[0100]

画像検出モードとは、参照画像を検出するか否かを指定するパラメータである。セル部は同一パターンの繰り返しからなるので、事前にセル部の画像を撮像して記憶しておくことにより、欠陥ID毎に毎回参照画像を検出する必要はなく、記憶した画像を繰り返し参照画像として使用することができる。参照画像を新たに検出する場合には、検査対象となる半導体ウエハを搭載したステージを所望の位置に移動させ、撮像領域に電子線を照射して検出するステップを経る必要があるために、記憶装置16に記憶した参照画像を繰り返し流用する場合に比べ、多くの時間を要する。従って、参照画像を流用するモードにおいては、検査時間を大幅に短縮することができるために有利である。以下では、参照画像を記憶し、流用するモードを『参照画像レスモード』、参照画像を欠陥ID毎に毎回検出するモードを『参照画像検出モード』という。被検査領域中のセル領域に対しては『参照画像レスモード』を、非セル領域に対しては『参照画像検出モード』を夫々設定する。これにより、検査時間を大幅に短縮することができる。

[0101]

以上のように、レイアウトデータに基づいて被検査領域をセル部と非セル部と に自動的に分割し、これら各領域で検査モードを切り替えることにより、検査時 間を短縮することができる。

[0102]

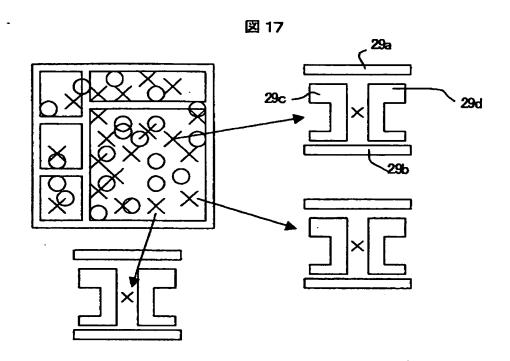

次に、図17~図19により、本発明による電子回路パターンの欠陥検査装置

及びシステムの第4の実施形態について説明する。

[0103]

この第4の実施形態の特徴は、特定のパターンで頻発する虚報の発生を抑制することである。

[0104]

図17にシンボル「×」で示すように、虚報を頻発させる問題の特定パターンがチップ内に散在している場合、チップスケールでの欠陥分布マップからは、虚報が同一の特定パターンに起因した虚報であることを読み取ることができない。そこで、レイアウトデータを利用して虚報が頻発するパターンを特定し、問題のパターン部における検査感度を変更することにより、虚報の発生を抑制できるようにするものである。

[0105]

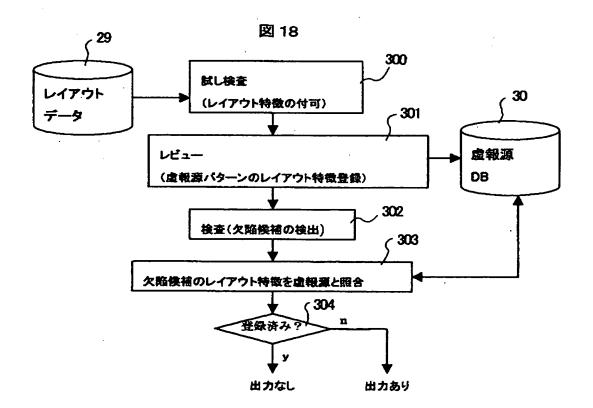

図18はこのための処理の流れを示すフローチャートである。

[0106]

同図において、まず、図25のステップ204に相当する試し検査実行時に(ステップ300)、欠陥が検出されると、レイアウトデータ29を参照して、この欠陥が発生したパターンに関する情報を取得する。具体的には、欠陥の座標と、欠陥近傍のパターンの位置、形状と、欠陥の位置関係である。図17に示す例では、シンボル「×」で示す欠陥の近傍のパターン29a, 29b, 29c, 29dの位置と形状、並びに欠陥との位置関係(即ち、パターン29a, 29b間、かつ、パターン29c, 29d間)がコード化されて欠陥に関する付帯情報として出力される。以下、これを欠陥のレイアウト特徴という。

[0107]

試し検査実行後、ユーザは、検出された欠陥毎に特定パターン起因の虚報か否かを教示する。ユーザが特定パターン起因の虚報と判断したものに対しては、これに対するレイアウト特徴が虚報を発生させる特定パターンのレイアウト特徴として登録される。以下、これを虚報源パターンデータベース30という。図17では、同じレイアウトのパターン部に虚報が生じたことを示している。

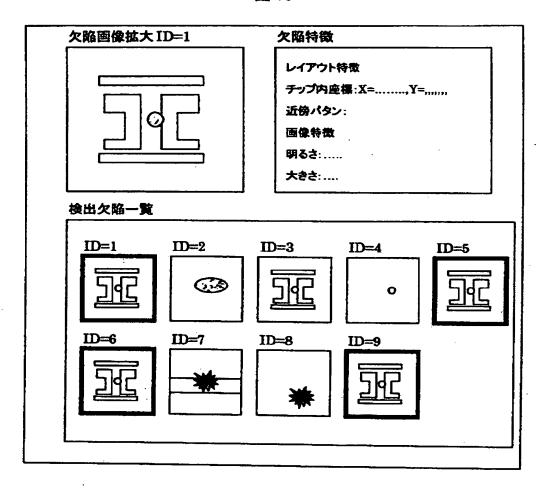

[0108]

図19はかかる教示用のユーザインターフェース画面の一具体例を示すものであって、ユーザがかかる教示用のユーザインターフェース画面での検出した欠陥の一覧表示の中から特定パターンに起因する虚報を選択することにより、特定パターンに起因した虚報のレイアウト特徴が虚報源データベース30に登録される(ステップ301)。

## [0109]

次に、検査実行時には(ステップ302)、レイアウトデータを参照して、検出した欠陥候補のレイアウト特徴を算出する。そして、虚報源パターンデータベース30に算出したレイアウト特徴が虚報源として登録されているか否か検索し(ステップ303)、既に登録されていれば(ステップ304)、虚報と判定し、欠陥として出力しない。図18では、虚報源となる特定パターンでの欠陥は検出しないこととしているが、例えば、虚報源となる位置でも、一定以上の大きさの欠陥は欠陥として出力する、あるいは一定以上の明るさの欠陥は欠陥として出力するなど、欠陥としての出力条件を特定パターン部で変えてもよい。

## [0110]

以上により、レイアウトデータを利用して虚報が頻発するパターンを特定し、 問題のパターン部での虚報を抑制することができる。

## [0111]

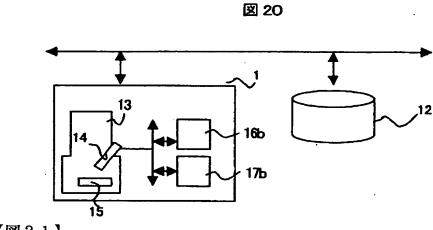

図20は本発明による電子回路パターンの欠陥検査装置及びシステムの第5の 実施形態を示す構成図であって、16bは記憶装置、17bは画像処理コンピュータであり、図9に対応する部分には同一の符号を付けている。

## [0112]

この第5の実施形態は、図9に示した第1の実施形態と同様に、被検査領域(例えば、図10での被検査領域19)を検査パラメータの異なる部分検査領域に分割するが、さらに、検査パラメータをかかる部分検査領域毎に自動的に最適化するものである。部分検査領域が多数になる場合、特に重要となる。

#### [0113]

図20において、画像処理コンピュータ17bと記憶装置16bとは、図9に おける画像処理コンピュータ17と記憶装置16と同様の機能を有するが、さら に、記憶装置16bは検出した画像も記憶し、画像処理コンピュータ17bは記憶装置16bに記憶された画像に対して処理を行なう機能も有するものである。 つまり、画像検出動作を伴わなって画像の記憶が行なわれ、この記憶された画像に対するオフライン画像処理も行なわれるのである。

## [0114]

検査実行時には、画像検出器14は被検査対象の半導体ウエハ15の画像を検出し、検出された画像に対して画像処理コンピュータ17bが記憶装置16bも用いて画像処理を実行し、その欠陥を検出して出力する。一方、検査パラメータ調整時には、画像検出器14が検出した画像は一旦記憶装置16に記憶される。画像処理コンピュータ17は、以下で説明するように、検査パラメータを部分領域毎に自動的に最適化する。

## [0115]

検査パラメータの自動最適化は、現状でのマニュアル操作のプロセスを自動化するものである。マニュアル操作によるパラメータ最適化においては、始めに、ユーザが検査パラメータの調整条件を仮設定する。本来、虚報を検出することなく、検出が必要な欠陥を全て検出することが望ましいが、実際には、感度を高く設定すると、実欠陥と同時に相当数の虚報も含まれてくる。そこで、最初の試し検査時には、感度を必要以上に若干高くして試し検査を実行し、その結果、検出欠陥総数が虚報も含めて一定以下の個数に収まるように、感度を下げながら試し検査を再実行する操作を繰り返す。以上のステップは、次のように整理できる。

#### [0116]

- (1)検査条件の初期値を設定する

- (2) 記憶した検出画像群に対し、仮設定した検査条件で画像処理を実行する

- (3)検査結果をパラメータの収束条件と比較する。ここで、パラメータの収束 条件として、例えば、次の例が挙げられる。

- (i)検出欠陥総数が一定個数以下を満たす範囲での検出感度最大

- (ii)検出欠陥密度が一定以下を満たす範囲での検出感度最大

- (iii) 虚報率が一定以下を満たす範囲での検出感度最大

- (iv) 指定した複数の欠陥点について検出率が一定以上を満たす範囲での検出

## 感度最小

- (4) 収束条件を満たしていればパラメータの調整を終了する

- (5) 収束条件を満たしていなければ、パラメータを事前に決定した量を変化させ、上記(2) からの処理を再実行する。

[0117]

以上のステップは、ユーザが事前に次の(1)~(3)、即ち、

- (1)検査パラメータの初期値

- (2)検査パラメータ調整の収束条件

- (3) 収束条件を満たさない場合の検査パラメータの変更量 を設定しておくことにより、自動化が可能である。

[0118]

図21はこの第5の実施形態における検査条件の設定画面を示している。ユーザが検査パラメータの初期値や検査パラメータの収束条件を各部分検査領域に対して設定することにより、自動的に検査パラメータが最適化される。

[0119]

#### 【発明の効果】

以上説明したように、本発明によれば、被検査領域の部分検査領域への分割を 検査条件の違いによって行なうものであるから、部分検査領域の設定工数を大幅 に低減することができ、被検査領域をかかる部分検査領域毎に最適な検査条件で 検査することができる。

[0120]

また、検出感度をパターンの最も稠密な部分に合わせて検査を行なうことによる検出欠陥数の爆発を回避できる。

【図面の簡単な説明】

【図1】

本発明による電子回路パターンの欠陥検査管理システムの第1の実施形態を示すプロック図である。

【図2】

レイアウトパターンの説明図である。

# 【図3】

チップ内のモジュール配置例を説明する図である。

## 【図4】

図1に示した第1の実施形態での検査パラメータ設定画面の一具体例を示す図である。

### 【図5】

本発明による電子回路パターンの欠陥検査管理システムの第2及び第3の実施 形態を示すブロック図である。

## 【図6】

本発明による電子回路パターンの欠陥検査管理システムの第3の実施形態での 検査パラメータ設定画面の一具体例を示す図である。

## 【図7】

図6に示した検査パラメータ設定画面の部分検査領域を再編集した検査パラメ ータ設定画面のセル領域設定画面を示す図である。

#### 【図8】

レイアウトパターンを説明するための図である。

## 【図9】

本発明による電子回路パターンの欠陥検査装置及びシステムの第1の実施形態 を示すブロック図である。

#### 【図10】

図9に示した実施形態における検査パラメータ設定画面の一具体例を示す図で ある。

## 【図11】

図9に示した実施形態における被検査領域の分割方法の一具体例を示す図である。

## 【図12】

図9に示した実施形態における被検査領域の分割方法の他の具体例を示す図で ある。

## 【図13】

図9に示した実施形態でのレイアウトデータとレビュー結果とを検査パラメータ設定画面上に重ね合わせて表示した様子を示す図である。

【図14】

本発明による電子回路パターンの欠陥検査装置及びシステムの第2の実施形態 を示すブロック図である。

【図15】

図14に示す実施形態における検査パラメータ設定画面を示す図である。

【図16】

本発明による電子回路パターンの欠陥検査装置及びシステムの第3の実施形態 を示すブロック図である。

【図17】

特定パターンに起因した虚報が散在する様子を説明する図である。

【図18】

本発明による電子回路パターンの欠陥検査装置及びシステムの第4の実施形態 での処理の流れを説明するフローチャートである。

【図19】

図18に示す処理での虚報源パターンの教示用インターフェース画面の一具体 例を示す図である。

【図20】

本発明による電子回路パターンの欠陥検査装置及びシステムの第5の実施形態 を示すブロック図である。

【図21】

図20に示す実施形態における検査パラメータ設定画面を示す図である。

【図22】

従来のパターン検査装置の一例を示す構成図である。

【図23】

図8における比較器の比較演算処理についての説明図である。

【図24】

従来の検査パラメータ設定画面の一例を示す図である。

# 【図25】

電子回路パターンの欠陥検査におけるパラメータ調整手順を示すフローチャートである。

# 【符号の説明】

- 1 パターン検査装置

- 2 設計情報サーバ

- 3 LAN

- 4 ウエハマップ

- 5 セル領域設定画面

- 6,7 部分検査領域

- 8 欠陥レビュー装置

- 9 セル部

- 10 非セル部

- 11 欠陥(虚報)群

- 12 部分検査領域

- 13 走查型電子顕微鏡

- 14 画像検出器

- 15 半導体ウエーハ

- 16, 16a, 16b 記憶装置

- 17, 17a, 17b 画像処理コンピュータ

- 18 検査パラメータ設定画面

- 19 被検査領域

- 19a~19d 部分領域

- 20 ウエハマップ

- 21 格子

- 23 配線

- 24 配線密度算出点

- 25 仮想的な円

- 27a~27d 機能ブロック

## 特2001-294482

- 28 検査パラメータ検索ボタン

- 29a~29d パターン

- 120 ステージ

- 121 半導体ウエハ

- 122 検出光学系

- 123 検出器

- 124, 125 メモリ

- 126 比較器

- 127 検査対象箇所

- 128 参照箇所

【書類名】

図面

【図1】

【図2】

図2

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

図 11

【図12】

図 12

【図13】

図 13

【図14】

【図15】

図 15

【図16】

【図17】

【図18】

【図19】

図 19

1 5

【図20】

【図21】

図 21

【図22】

図 22

【図23】

図 23

【図24】

図 24

【図25】

# 【書類名】 要約書

## 【要約】

【課題】 検査対象領域を局所的に最適な検査条件で検査して虚報の低減,検査時間の短縮を図かり、検出欠陥数の爆発を回避して致命性欠陥の管理を容易にする。

【解決手段】 設計情報サーバ2には、半導体ウエハのマスク作成時に用いられる汎用のレイアウトデータが蓄積されており、このレイアウトデータを参照してパターン検査装置1で検査する検査対象領域をセル部、非セル部の部分検査領域に分割し、各部分検査領域毎に検査パラメータを設定する。欠陥レビュー装置8は、パターン検査装置1の検査結果を取り込むが、欠陥画像を取り込む際、その欠陥がセル部、非セル部、パターン密集部などのいずれに発生したものであるかをレイアウトデータに基づいて判定し、その判定結果に応じてこの欠陥の撮影倍率などの検査パラメータを設定し、致命性の管理基準を設定する。

【選択図】 図5

# 出 願 人 履 歴 情 報

識別番号

[000005108]

1. 変更年月日 1990年 8月31日

[変更理由] 新規登録

住 所 東京都千代田区神田駿河台4丁目6番地

氏 名 株式会社日立製作所